Chapter 12 - 6. MOSFET의 기생 BJT

n-MOSFET은 소스/기판/드레인이 n+/p/n+ 형태로 연결되어 있다. 이는 MOSFET에 기생 BJT가 병렬 연결된 것과 같아서 MOSFET의 전기적 특성을 따르지 않을 때가 있다. 또한 반도체 소자의 소형화를 위해 MOSFET의 게이트 길이는 점점 짧아지는데 게이트 길이가 짧아질수록 기생 BJT의 동작 특성이 뚜렷해진다. 예를 들면 눈사태 붕괴 현상이 발생할 정도의 큰 전압이 아님에도 불구하고 기생 BJT의 영향으로 인해 드레인 전류가 급격하게 증가하는 때가 있다.

기생 BJT의 특성에 따른 활용

- 기생 BJT의 특성을 억제하는 경우

MOSFET 본래의 기능을 유지하여 MOSFET 또는 CMOS 등으로 이루어진 소자를 안정적으로 동작시키기 위한 회로

- 기생 BJT의 특성을 활용하는 경우

커패시터가 없는 DRAM(capacitorless DRAM), 반도체 소자를 정전기로부터 안전하게 보호하는 회로

- 기생 BJT에 의한 드레인 전류 스냅백(snapback) 현상

드레인 전류 스냅백(snapback) 현상

채널이 짧은 MOSFET에 큰 드레인 전압이 인가되었을 때 기생 BJT의 동작에 의해 드레인 전류가 제어 불가능한 상태가 되는 현상

채널 길이가 짧을수록 작은 드레인 전압임에도 불구하고 드레인 전류 스냅백(snapback) 현상이 잘 나타난다.

드레인 전류 스냅백(snapback) 현상 원리

1) 채널이 짧은 MOSFET에 큰 드레인 전압이 인가되면 드레인 부근에서 전자-정공 켤레 생성

2) 정공이 기판으로 이동하여 기생 BJT형성, 소스와 기판 양단에 순방향 전압이 인가된 것과 같이 작용

3) 소스와 기판은 각각 BJT에서의 에미터와 베이스 역할

4) 전자는 소스에서 기판으로 이동 가능하고, 기판에서 드레인으로 이동 가능

위 과정으로 큰 누설전류가 흐르게 된다.

드레인 전류 스냅백(snapback) 현상을 막기 위한 방법

- 낮게 도핑된 드레인(LDD) 만들기

- 베이스 영역의 폭에 해당하는 채널 길이 늘이기

- 과열 이동전하 생성 억제를 위해 드레인 전압 낮추기

- 기판의 소수 캐리어 평균 수명과 확산 길이를 짧게 하기

- 완전히 공핍된 Si층으로 형성된 절연 기판 사용

- 기생 BJT에 의한 CMOS에서 드레인 전류 래치업(latch-up) 현상

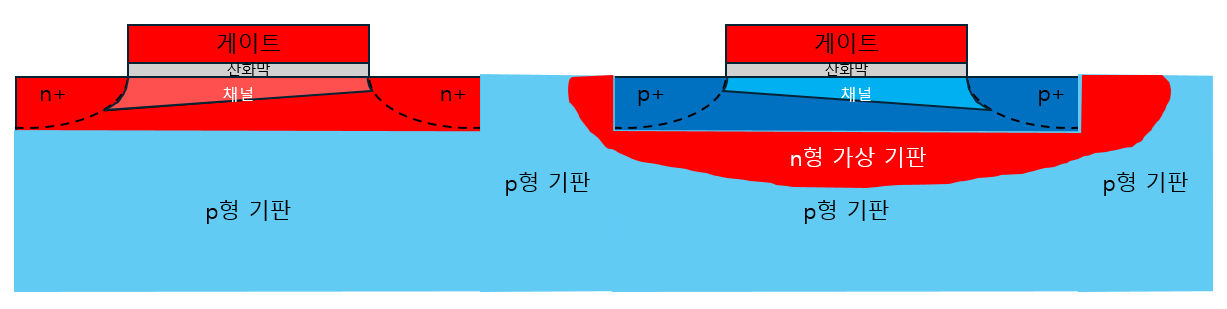

CMOS란 n-MOSFET과 p-MOSFET을 함께 사용하는 상보형(complementary) MOSFET이다.

CMOS에서 드레인 전류 래치업(latch-up) 현상은 기판을 공유하는 CMOS에서 n-MOSFET의 기생 BJT와 p-MOSFET의 기생 BJT가 함께 전류를 증폭하는 것이다.

CMOS에서 드레인 전류 래치업(latch-up) 현상 원리

드레인 전류 스냅백(snapback) 현상과 같은 원리

1) n-MOSFET에서 소스(n+)와 기판(p) 사이 흐르게 되는 기판 전류

2) p-MOSFET에서 소스(p+)와 n형 가상 기판(n) 사이 흐르게 되는 기판 전류

위의 두 전류가 생성된 뒤 합쳐지는 전류 증폭이 된다.

CMOS에서 드레인 전류 래치업(latch-up) 현상을 막기 위한 방법

- n-MOSFET의 채널 길이를 늘이기

- n형 가상 기판의 두께 두껍게 하기

- p형 기판만을 사용하지 않고 p형 가상 기판과 n형 가상 기판 모두 이용하기

- 완전히 공핍된 Si층으로 형성된 절연 기판 사용

요약

MOSFET의 기생 BJT는 MOSFET에 영향을 미치는데, 게이트 길이가 짧아질수록 이 영향이 뚜렷해진다.

기생 BJT의 특성을 억제하거나 활용하는 회로 설계는 MOSFET / CMOS 집적회로의 안정성에 영향을 미친다.

드레인 전류 스냅백 현상과 래치업 현상은 기생 BJT의 동작으로 발생하며 이를 막기 위한 다양한 방법이 있다.

'반도체 기초 이론 정리' 카테고리의 다른 글

| 반도체 기초 Chapter 13 - 1. 접합형 전계효과 트랜지스터(JFET, MESFET 등) 특징 (0) | 2024.04.04 |

|---|---|

| 반도체 기초 Chapter 12 - 7. MOSFET의 소형화로 인한 특성 변화 (0) | 2024.04.03 |

| 반도체 기초 Chapter 12 - 5. 큰 드레인 전압이 인가된 MOSFET의 특성 (0) | 2024.04.01 |

| 반도체 기초 Chapter 12 - 4. 기판전압에 의한 드레인 전류와 임계전압 변화 (0) | 2024.03.31 |

| 반도체 기초 Chapter 12 - 3. MOSFET의 특성 (0) | 2024.03.30 |